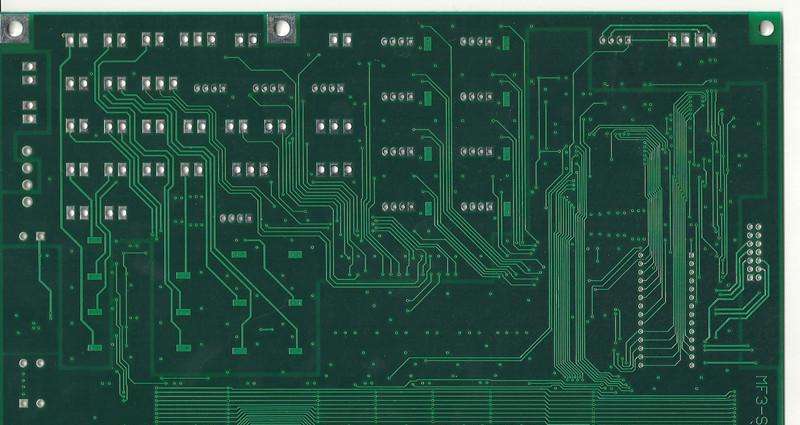

大家在看到一个pcb成品时,内心是不是充满着自豪呢?是不是觉得人类的智慧特别伟大呢?其时有这样的想法都是正常的,毕竟pcb的出现无疑是一件十分棒的事情。但是在利用它之前,大家是否知道它的出现不是一瞬间的,相反它需要经过pcb设计才可以得出来。同样,专业的设计师在针对pcb设计的过程中会注意细节的方方面面,只有严格把关好这些细节上的事项,只有合理地进行布线连接才可以顺顺利利的让电路板腾空出世。

下面的内容是东莞市博远电子有限公司针对pcb设计的一些经验分享,希望对有需求的人提供一些帮助:

首先,pcb设计师不是只会设计的,他们需要掌握的知识有很多,至少要十分了解各类电子元器年的工作原时,只有了解它们,只有知道它们彼此之间的关联,只有了解它们之间的影响,才能够更加清楚地知道输入与输出的传输标准,而且任何优秀成功的电子产品都是以原理图作为依托的,所以pcb设计师对版图技术了解到位,才能够避免后续工作中发生重大问题。

然后,pcb设计过程中的噪声处理也迫在眉睫。目前要解决噪声问题,那么就需要从三个方向入手。振铃和串扰的问题,特别是一些关键性的信号要注意下串扰事项,合理地运用好差分信号,走线时利用好差分对走线,才可以从根本上消除感应的问题,并且保证路径的顺利进行,避免发生反弹的噪声等等;pcb设计过程中,阻抗匹配度也是个要把关起来的问题,这一点是无比重要的,毕竟很多时间两根线间的走线还是十分靠近的,所以pcb设计师们需要事先同厂家商定好使用怎样的阻抗才行;pcb设计过程中的电容使用事项,合理采用一下去耦电容器更有助于减小线路板的电源和地平面之间的电感,只有尽量控制好这点才可以保障后面工作的顺利。

其次,pcb设计的过程中十分有可能会经受着时钟信号干扰的相关问题,大抵上的原因还是钟线过分长千万的,所以pcb设计的过程中需要避免使用多个层来传输时钟,并且不要在时钟线上有过孔,因为过孔将增加走线的阻抗变化和信号的反射。其次,如果必须用内层来布设时钟,那么上下层应该使用地平面来减小延迟。再次,如果电源平面上不幸引入时钟噪声会增加PLL抖动,那么在修改PCB设计时可以创建一个“电源岛”,这种技术可以利用金属平面中的较厚蚀刻来实现PLL模拟电源和数字电源的隔离。

最后一点,东莞市博远电子有限公司的工程师要讲的是有关于pcb设计时的布局问题,大家都了解到pcb设计过程中最关键的还是连接,只有选择恰当的、直接的路径,才能够收获更好的效果,而这方面知识的掌握可以获得更大的快乐,那么为什么不重视起来呢!